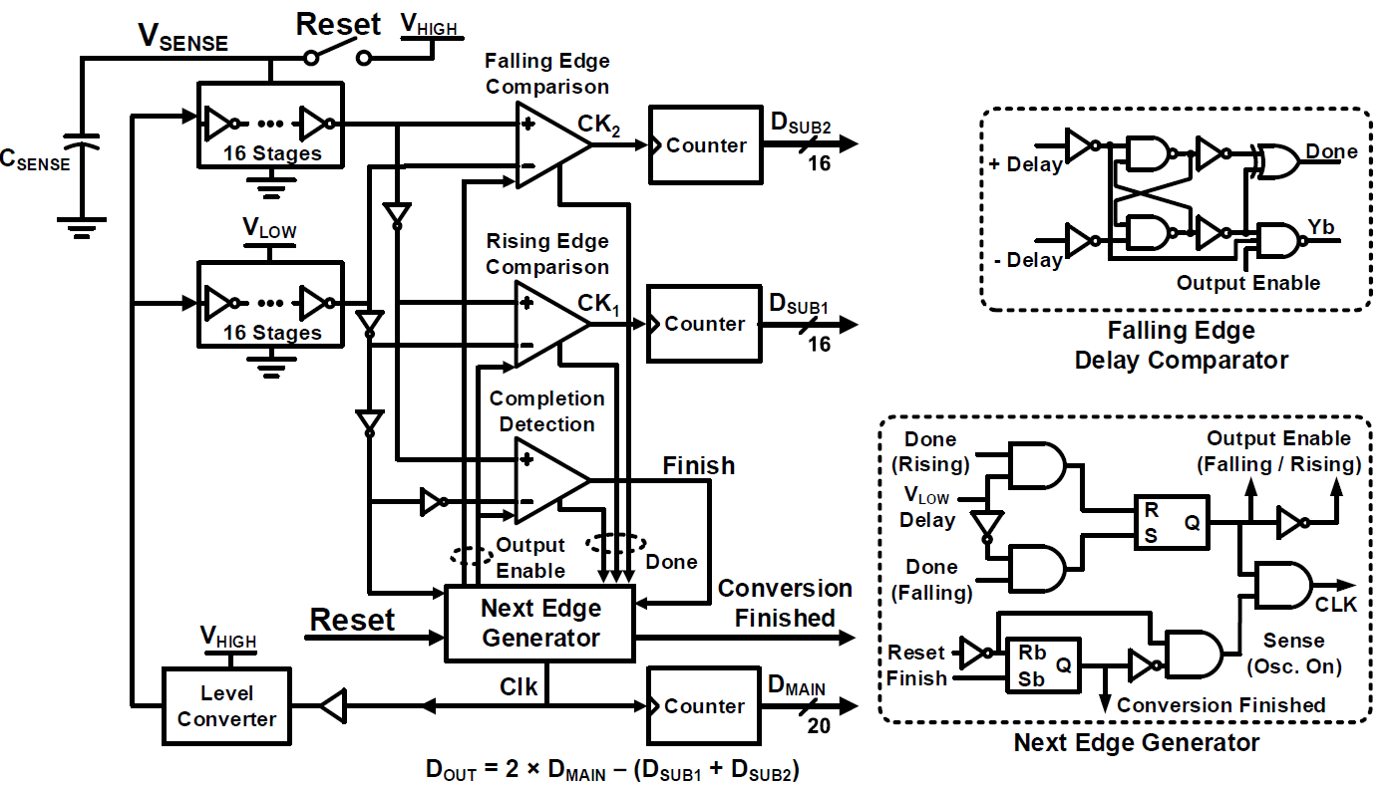

To design synthesizable sensor interfaces, we have identified a new capacitance to digital converter (CDC) that is constructed from standard cells, making automatic verilog generation and synthesis possible. It consists of a ring oscillator, a reference delay, a comparator, and a counter. The sensed capacitance is converted to a digital code without any analog circuits like amplifier and an ADC.

Figure 2: CDC Block Diagram

The CDC input capacitance range is essentially unlimited, constrained only by counter size. Below are the targeted user spec ranges for which the CDC_GEN tool can output a correct design in TSMC 180nm and TSMC 65nm technology nodes:

CDC Generator Input Spec Ranges

| Resolution | 1 bit – 8 bits |

| Freq. of operation | 100KHz – 10MHz |

IDEA & POSH Integration Exercises – January 2019 Demo

Video 1 shows the generation of a CDC design using the CDC_GEN tool. Based on the user spec input, the design parameters (number of cells and stages) are changed automatically. The final design is then synthesized and placed to generate a completely placed CDC.

Video 1: CDC_GEN tool