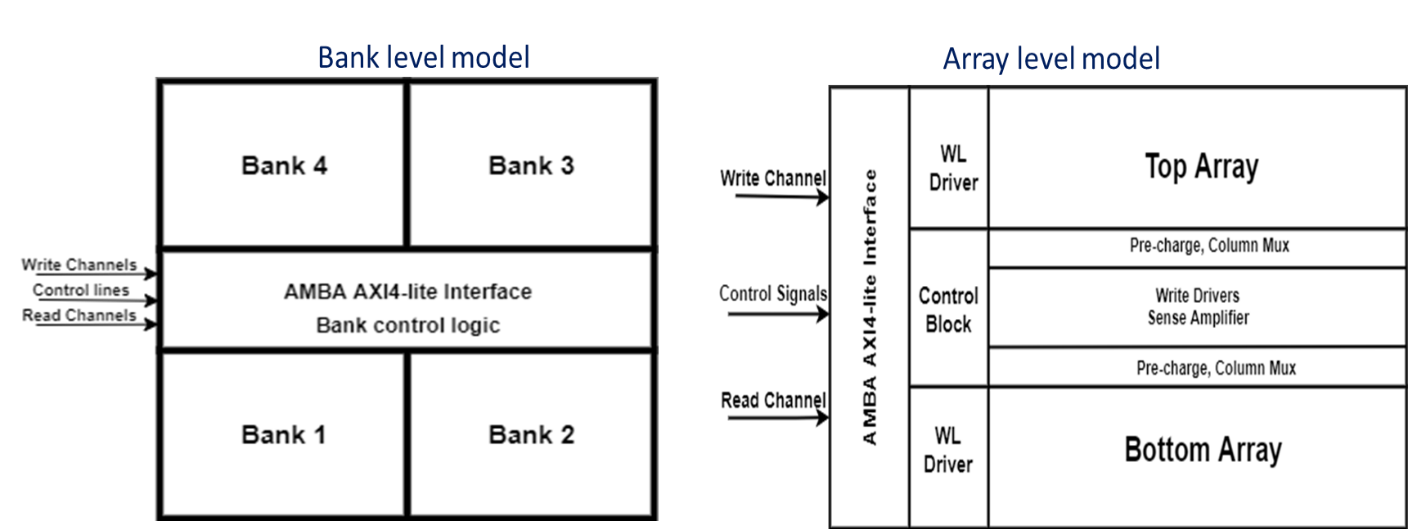

Memory generator generates a synthesizable memory macro by combining the auxiliary cell models and simulation-based optimization of the low-level components to determine the SRAM configuration (#banks, #rows per bank and #columns per bank) accounting the key constraints like performance, power, area and yield. A parameterized verilog netlist is then generated depending on the implementation hierarchy (Figure 1) computed based on the cost function of the performance and yield.

Figure 1: Different hierarchical levels of memory generation implementation

“MEM_GEN” tool that automates the optimization and generation of synthesizable memory satisfying a range of user specifications is developed to achieve a technology agnostic memory design platform. Below are the targeted user specifications of the memory (more user specs are added as the tool matures) for which “MEM_GEN” tool creates the memory TSMC 65nm and IBM 130nm PDK’s.

Memory Generator

| Operating Voltage | 0.5V – 0.8V |

| Word Size | 32 bits and 64 bits |

| Memory Size | 16kb |

IDEA & POSH Integration Exercises – January 2019 Demos

Video 1 demonstrates the generation of the synthesizable memory macro by exploring the Pareto design space satisfying the user specifications of the TSMC 65nm PDK, 8KB memory capacity, 32 bit word size and operating voltage of 0.5v.

Video 1: MEM_GEN tool