The objective of this part is to intelligently design systems from high-level user input and estimate the performance of the designed system. This is done by implementing a wrapper tool around Socrates tool that takes in block level SoC designs scripts as user inputs. The user input includes the functionality specs of each block, and constraints on power/area of the whole SoC.

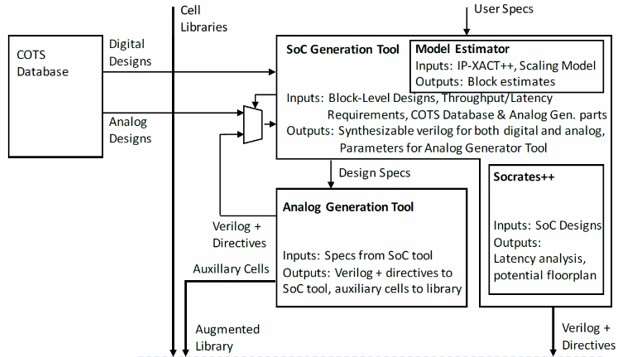

In “Correct by construction” design process, the first step of SoC synthesis is finding the desired blocks based on user input script. This searching process begins with fixed components. If the tool is not able to find the desired IP in the target technology node, it will call “Synthesizable Analog Generator” if the IP category is included in its domain. Otherwise, the tool tries to estimate the performance of the IP using technology model estimator. Since searching among existing IPs is way less time consuming, the tool will populate a new IP with IP-XACT++ format in the database. This avoids re-generating or re-estimating if the tool wants to use a similar IP another time. Once everything including whole SoC schematic, and P&R is done the tool will add this SoC to our COTS database to use it in the future if it is needed and not repeating this entire process again. The correct by construction design is shown in Figure 1.

Figure 1: Correct by construction Design

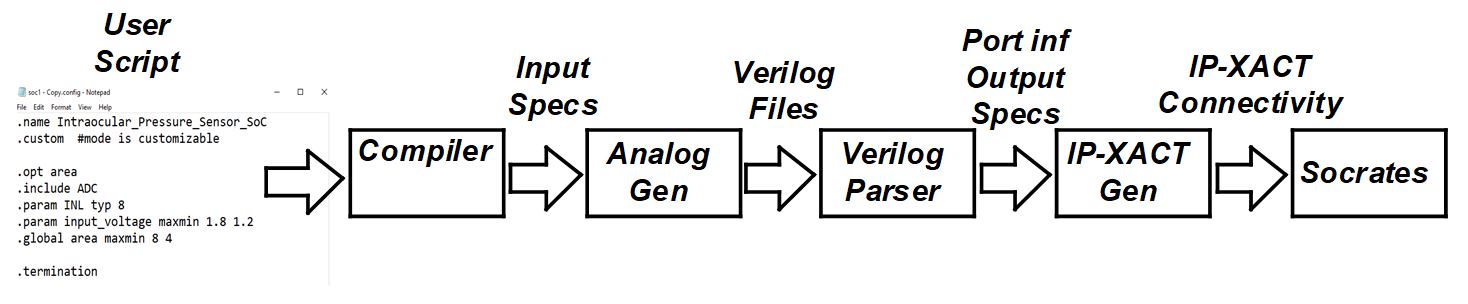

A final design RTL will be generated along with associated timing constraints and relative/structured placement scripts to be used in synthesis/APR. The design process will also identify potential timing critical paths and insert latency insensitive interfaces that allow register slices to be added if timing cannot be met. In addition, the wrapper tool will also output the configuration parameters for the analog blocks in the system. The analog tools will be run and candidate designs are fed back to the wrapper. The final analog design output will be a structured netlist of the block. Figure. 2 shows this procedure.

Figure 2: Correct by construction flow

IDEA & POSH Integration Exercises – January 2019 Demos

Demo 1: Correct by Construction Design

Video 1 shows the generation of IP-XACT++ and Verilog files from a sample user’s input script in a correct by construction flow using ADPLL generator.

Video 1: Correct by Construction Design

Demo 2: Socrates Integration

Video 2 shows importing IP-XACT++ of blocks, integration of a sample SoC and the generation of IP-XACT++ and Verilog files of whole SoC using the Socrates tool.

Video 2: Socrates Integration