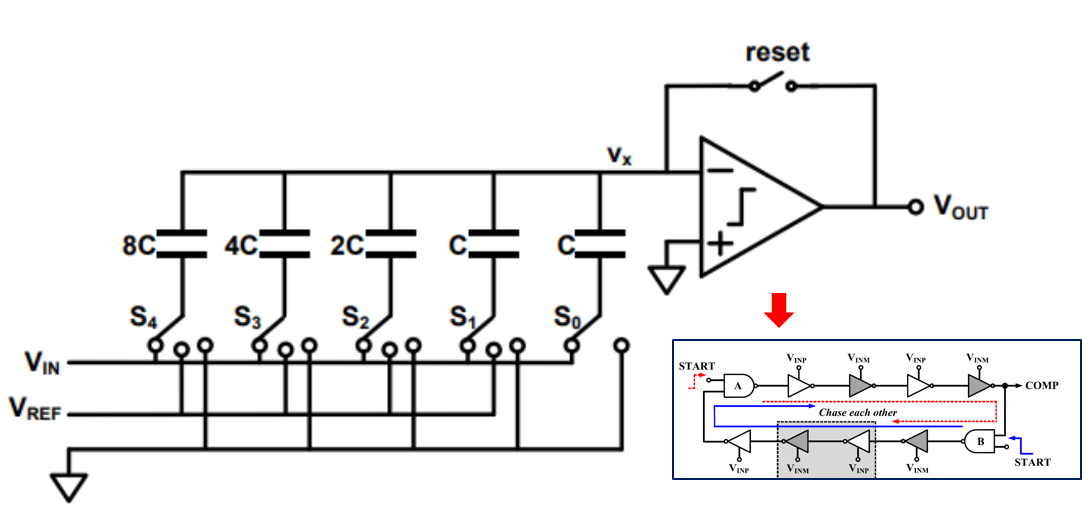

For synthesizable data conversion, successive approximation analog to digital converters (SAR ADC) are the preferred topology as it does not require complex analog circuits. It consists of a number of unit capacitors, switches, and SAR logic. These are digital circuits and hence facilitate the design of a canonical unit cell. However, since the comparator in a SAR ADC is the only analog circuit, this becomes the key block in developing a synthesizable SAR ADC.

Figure 1: ADC Block Diagram

We have developed a “Edge Pursuit Comparator” structure that leverages a standard library cell characteristics to automate the ADC design process. The comparator auxiliary cell consists of two NAND gates and several inverter delay cells like a ring oscillator. Moreover, the implemented comparator has an additional advantage that it inherently adjusts its energy consumption without any external control because the collapse speed is dependent on the difference of the input voltage.

Below are the targeted user spec ranges for which the ADC_GEN tool can output a correct design in TSMC 180nm and TSMC 65nm technology nodes:

ADC Generator Input Spec Ranges

| Resolution | 1 bit- 8 bits |

| Freq. of operation | 100KHz – 10 MHz |